atpg test pattern compression|atpg vs logic bist test : service Creation of the compressed pattern from the original ATPG test pattern consists of solving a set of linear equations based on the ring generator polynomial and the phase shifter connections. . As formigas do filme MIB Homens de Preto são Anelídeos, que na verdade é um tipo de animal que existe na vida real. Na história seus nomes são Neeble, Geeble, Sleeble e .

{plog:ftitle_list}

webAumente suas vendas com Stanley O melhor Distribuidor de produtos Stanley no Brasil – Atacado e Presentes Corporativos Soliticitar orçamento Aproveite a alta demanda em 2023 e aumente suas vendas com o Copo Térmico STANLEY: Um produto INDISPENSÁVEL para quem busca praticidade e qualidade no dia a dia. Com o aumento das .

Two test strategies are used to test virtually all IC logic: automatic test pattern generation (ATPG) with test pattern compression and logic built-in self-test (BIST). This article.

Some ATPG-based test data compression schemes borrow either the front-end .

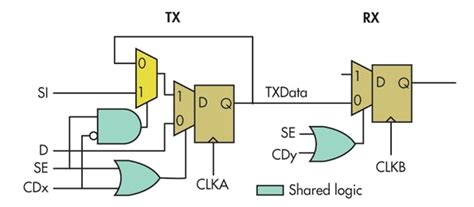

Some ATPG-based test data compression schemes borrow either the front-end PRPG random data generation or back-end data compaction structures or both from BIST. OPMISR is an example of a.Creation of the compressed pattern from the original ATPG test pattern consists of solving a set of linear equations based on the ring generator polynomial and the phase shifter connections. .Test compression is a technique used to reduce the time and cost of testing integrated circuits. The first ICs were tested with test vectors created by hand. It proved very difficult to get good coverage of potential faults, so Design for testability (DFT) based on scan and automatic test pattern generation (ATPG) were developed to explicitly test each gate and path in a design. These techniques were very successful at creating high-quality vectors for manufacturing test, with exc.

Unlike testing deterministic circuits, where each test pattern is applied only once, testing probabilistic circuits requires multiple pattern repetitions for each test pattern. In this paper, . Hybrid ATPG/LBIST test points reduce deterministic test pattern counts and improve random testability, and the insertion algorithm is much faster than previous algorithms. For more information, download our whitepaper, .In this paper, we propose a novel and efficient compression-aware ATPG method to significantly boost the performance of ATPG and reduce pattern count. The proposed approach first .This algorithm reorders and compresses test patterns previously generated in an ATPG in such a way that they are well suited for decompression by the scan chains in the embedded tester .

logic bist and atpg

In this paper we propose a new method of test patterns compression based on a design of a dedicated SAT-based ATPG (Automatic Test Pattern Generator). An optimal compression level, λ, minimizes test cost. x C is the compression level needed to fit a complete scan ATPG pattern set, P C , into the fixed amount of tester memory. TATR denotes the economic benefits of . Hybrid test points are also better than EDT test points at reducing ATPG pattern count. Table 2 illustrates. Table 2. Comparison of ATPG pattern count with three types of test points. The ATPG baseline columns show the .

how does atpg work

ATPG (Automatic Test Pattern Generation and Automatic Test Pattern Generator) is an EDA method/technology used to find an input or test sequence. When applied to a digital circuit, ATPG enables automatic test equipment to distinguish between the correct circuit behavior and the faulty circuit behavior caused by defects. The generated patterns are used to test. » read moreUnlike testing deterministic circuits, where each test pattern is applied only once, testing probabilistic circuits requires multiple pattern repetitions for each test pattern. In this paper, we propose an ATPG algorithm for probabilistic circuits. We use specialized activation and propagation methods to reduce pattern repetitions. Also, we propose to accumulate .

LogicVision is a leading provider of Built-in-Self-Test ( BIST) technologies for testing today's System-on-Chip (SoC) designs. The combination of Mentor's industry-leading Automated Test Pattern Generation ( ATPG) and embedded test pattern compression technology, and LogicVision's BIST products, enables Mentor to provide customers with comprehensive and .EST: The new frontier in automatic test-pattern generation. John Giraldi. 1991. download Download free PDF View PDF chevron_right. Biology, ecology, and uses of the medicinal plant Sesamum alatum. . 20 5.2 Software Test Pattern Compression Since the care bit density of the test patterns is low, it is possible to pack multiple non-conflicting .

Modus ATPG supports hierarchical test, low-power ATPG with scan and capture toggle count limits, and distributed test pattern generation with near-linear runtime scalability. Modus Diagnostics includes single- and multi-die volume diagnostics, both with physical defect location callout and root-cause analysis. Test compression is a technique implemented for test compression. It creates & embeds the test compression logic into the design. It further extends ATPG to generate compressed test patterns .aware design-for-test (DFT), automatic test pattern generation (ATPG), and silicon diagnostics tool. Using the Cadence Modus DFT Software Solution you can experience an up-to-3X reduction in test time using its patented physically aware 2D Elastic Compression architecture, without any impact on fault coverage or chip size. Features and Benefits

The SFFs have uncompressible values logic-0 and logic-1 in many or most of the patterns contribute to the TDV. In the proposed new scan compression (NSC) architecture, SFFs are analysed from Automatic Test Pattern Generation (ATPG) patterns generated in . Improvements that have been done on the test pattern compaction and compression algorithm called COMPAS, which is capable to compress data generated by concurrently working ATPG processes, are reported here. This paper describes a test data compression method based on pattern overlapping. We report here improvements that have .Rapid increases in the wire-able gate counts of ASICs stress existing manufacturing test equipment in terms of test data volume and test capacity. Techniques are presented in this paper that allow for substantial compression of Automatic Test Pattern Generation (ATPG) produced test vectors. We show compression efficiencies allowing a more than 10-fold reduction in .

EDT Test Points are a new type of test point technology that gives big payoffs in pattern count reduction over what you can get with the best ATPG compression. Figure 2. Adding a test point (CP) reduces pattern count by providing more .To maximize throughput, automatic test pattern generation (ATPG) can be distributed across multiple processors. Lower test time and pattern count Built on the patented Embedded Deterministic Test (EDT) technology, Tessent TestKompress reduces both test time and pattern volume by several orders of magnitude without any loss in fault coverage. In particular, much has been published on new techniques for on-chip compression of automatic test pattern generation (ATPG) in order to reduce ever-growing pattern sizes. These techniques — some oddly named using the term built-in self test (BIST) — do indeed represent improvements on existing ATPG methodologies.

Rubber compression stress relaxation Tester mfg

在跑ATPG 时 try flow/分析coverage时,一般会跑EDT & Bypass Mode ATPG,当然最终测试的pattern 还是选择压缩pattern。 多个mode ATPG都跑时可以通过对比去debug Test Coverage. 压缩比高导致 .

Scan is the internal modification of the design’s circuitry to increase its test-ability. ATPG stands for Automatic Test Pattern Generation; as the name suggests, this is basically the generation of test patterns. In other words, we can say . With scan ATPG compression, which is based on EDT technology, circuitry receives compressed data from the tester, decompresses it within the chip, and then compacts the response for verification. The . The past decade observed compression of test data as an effective method for reducing the volume of test data and test application time. In order to work with the increasing clock frequencies in a contemporary design, a low fill rate of care bits is exploited due to the result of combinational logic [].Hence, the fill rate of the every determined test pattern did not .

Generates high-coverage test patterns in hours instead of days; Lowers test time and cost with fewer patterns than existing solutions; Enables highly efficient utilization of hardware resources for ATPG

Test Compression Acknowledgements: Mil b d th l t t f ch8-1 Mainly based on the lecture notes of Chapter 6, “VLSI Test Principles and Architectures” . Force ATPG tool to generate patterns for broadcast scan ((y g g )by binding certain PI’s together) ch8 .``Implementing test compression without impacting design schedules Solution ``DFT MAX compression to reduce test data volume and test time ``TetraMAX® ATPG for DSM test pattern generation ``PrimeTime® static timing analysis for high-quality at-speed patterns Benefits ``Higher test quality than previously possible ``Lower cost of defect screening

Quantum circuit testing is essential for detecting potential faults in realistic quantum devices, while the testing process itself also suffers from the inexactness and unreliability of quantum operations. This paper alleviates the issue by proposing a novel framework of automatic test pattern generation (ATPG) for robust testing of logical quantum .

Overall, the test problem is reduced to testing the small blocks of combinational logic between the sequential gates. Scan simplifies the test problem enough that automated test pattern generation (ATPG) tools can quickly and efficiently create test patterns. In our observation, the test patterns generated by commercial ATPG tools in test compression mode still contain redundancy. To tackle this obstacle, we propose a post-flow static test compaction method that utilizes a partial fault dictionary instead of a full fault dictionary, and leverages a dedicated Pure-MaxSAT solver to re-compact the test .

In this paper we propose a new method of test patterns compression based on a design of a dedicated SAT-based ATPG (Automatic Test Pattern Generator). This compression method is targeted to systems on chip (SoCs)provided with the P1500 test standard. The RESPIN architecture can be used for test patterns decompression. The main idea is based on finding .of the patterns contribute to the TDV. In the proposed new scan compression (NSC) architecture, SFFs are analysed from Automatic Test Pattern Generation (ATPG) pat-terns generated in a scan mode. The identificationof SFFs to be moved out of the compression architecture is carried out based on the NSC. The method includes a ranking

First we apply reverse order fault simulation to remove redundant test patterns. This greatly reduces the test length. For further improvement, we apply several times of random order fault simulation.

difference between atpg and logic

14 de nov. de 2023 · Ator de 1,88 metro de altura foi escoltado por profissional de mais de 2,10 metros de altura. Grandão, mas nem tanto! Schwarzenegger fica “baixinho” perto .

atpg test pattern compression|atpg vs logic bist test